Industry Solutions Industry Solutions

|

|

|

An interface is defined independently from modules, between the keywords "interface" and "endinterface." Modules can use an interface the same as if it were a single port. In its simplest form, an interface can be considered a bundle of wires. Interfaces go far beyond just representing bundles of interconnecting signals, however. An interface can also include functionality that is common to each module that uses the interface. In addition, an interface can include built-in protocol checking.

Global declarations. Verilog has an implicit global name space which holds the names of modules and primitives. SystemVerilog makes this global space accessible to the user. Any declarations outside of a module boundary are in the global, or root, name space. All modules, anywhere in the design hierarchy, can refer to names declared in the root space. This allows global variables, type definitions, functions and other information to be declared, that are shared by all levels of hierarchy in the design.

Relaxed data type rules. The Verilog language has strict rules on where net data types (such as wire, wand, wor) must be used, and where variables (such as reg, integer) must be used. SystemVerilog relaxes these rules, allowing variable types to be used in almost any context. The relaxed rules make it much easier to write hardware models without concern about which data type class to use. Since variables do not have wired-logic resolution like net data types, semantic restrictions ensure that a variable cannot be driven by multiple output ports or multiple continuous assignments.

Data types. Verilog provides hardware-centric net and variable data types. These types represent 4-state logic values, and are used to model and verify hardware behavior at a detailed level. The net data types also have multiple strength levels and resolution functions for multiple drivers of the net. SystemVerilog adds several new data types, which allow hardware to be modeled at more abstract levels, using data types more intuitive to C programmers.

class " an object-oriented dynamic data type, similar to C++ and Java.

byte " a 2-state signed variable, that is defined to be exactly 8 bits.

shortint " a 2-state signed variable, that is defined to be exactly 16 bits.

int " a 2-state signed variable, similar to the "int" data type in C, but defined to be exactly 32 bits.

longint " a 2-state signed variable, that is defined to be exactly 64 bits.

bit " a 2-state unsigned data type of any vector width.

logic " a 4-state unsigned data type of any vector width, equivalent to the Verilog "reg" data type.

shortreal " a 2-state single-precision floating-point variable, the same as the "float" type in C.

void " represents no value, and can be specified as the return value of a function.

User defined types. SystemVerilog provides a method to define new data types using "typedef," similar to C. The user-defined type can then be used in declarations the same as with any data type.

typedef unsigned int uint;

uint a, b;

Enumerated types. SystemVerilog allows the creation of enumerated types, using a C-like syntax. An enumerated type has a value from a set of named values.

enum {red, green, blue} RGB;

enum logic 2:0 {WAIT=3'b001, LOAD=3'b010, DONE=3'b100} states;

SystemVerilog also provides several built-in methods for working with enumerated types. These methods allow, for example, incrementing to the next value in a type list, without having to know the name of that next value.

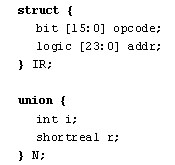

Structures and unions. SystemVerilog adds structures and unions, which allow multiple signals, of various data types, to be bundled together and referenced by a single name.

Fields within a structure or union are referenced using a period between the structure or union name and the field name, as in C.

IR.opcode = 1; //set the opcode field in IR

N.r = 0.0; //set N as floating point value

A structure can be assigned as a whole, using a list of values, the same as in C.

IR = {5, 200};

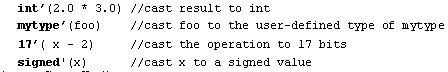

Casting. SystemVerilog adds the ability to change the type, vector size or "signedness" of a value using a cast operation. To remain backward compatible with the existing Verilog language, casting in SystemVerilog uses a different syntax than C.

Arrays. SystemVerilog enhances Verilog arrays in several significant ways, including the addition of dynamic arrays and associative arrays. Dynamic arrays are one-dimensional arrays where the size of the array can be changed dynamically. Built-in methods provide a means to set and change the size of dynamic arrays during run-time. Associative arrays are one-dimensional sparse arrays that can be indexed using values such as enumerated type names. Special built-in methods for working with associative arrays are provided: exists(), first(), last(), next(), prev() and delete().

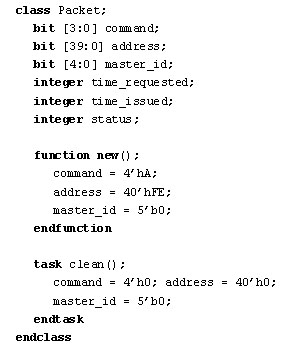

Classes. SystemVerilog adds object oriented classes to the Verilog language, similar to C++. A class can contain data declarations (referred to as "properties"), plus tasks and functions for operating on the data (referred to as "methods"). The properties and methods together define the contents and capabilities of an "object". Classes can have inheritance and public or private protection, as in C++.

Classes allow objects to be dynamically created, deleted and assigned values. Objects can be accessed via handles, which provide a safe form of pointers. SystemVerilog does not require the complex memory allocation and de-allocation of C++. Memory allocation, de-allocation and garbage collection are automatically handled, preventing the possibility of memory leaks.

An example of a SystemVerilog object definition is:

Next

|

|

Quick

Links...  Search...  Veritools.com

LOGIN...

Click Here for

fast access to whitepapers and datasheets and to receive electronic Veritools' news, services and upcoming events.

New

Downloads...

|

Home

Home