Industry Solutions Industry Solutions

|

|

|

Task and function enhancements. SystemVerilog adds several enhancements to the Verilog task and function constructs. Only a few of the enhancements are highlighted in this article.

Function return values can have a "void" return type. Void functions can be called the same as a Verilog task. The difference between a void function and a task is that Verilog functions have several semantic restrictions, such as no time controls.

Functions can have any number of inputs, outputs and inouts, including none.

Values can be passed to a task or function in any order, using the task/function argument names. The syntax is the same as named module port connections.

Task and function input arguments can be assigned a default value as part of the task/function declaration. This allows the task or function to be called without passing a value to each argument.

Task or function arguments can be passed by reference, instead of copying the values in or out of the task or function. Passing by reference allows the task or function to work directly with the value in the calling scope, instead of a local copy of the value. To use pass by reference, the argument direction is declared as a "ref," instead of input, output or inout.

Enhanced fork-join. In the Verilog fork-join statement block, each statement is a separate thread that executes in parallel with other threads within the block. The block itself does not complete until every parallel thread has completed. Therefore, any statements following a fork-join are blocked from execution until all the forked parallel threads have completed execution.

SystemVerilog adds fork-join_none, and fork-join_any blocks:

join_none " statements that follow the fork-join_none are not blocked from execution while the parallel threads are executing. Each parallel thread is an independent, dynamic process.

join_any " statements which follow a fork-join_any are blocked from execution until the first of any of the threads has completed execution.

Inter-process synchronization.SystemVerilog provides three powerful ways for synchronizing parallel activities within a testbench or abstract model: semaphores, mailboxes, and enhanced event types.

A semaphore is a built-in object class. Semaphores serve as a bucket with a fixed number of "keys." Processes using semaphores must procure one or more keys from the bucket before they can continue execution. When the process completes, it returns its keys to the bucket. If no keys are available, the process must wait until a sufficient number of keys have been returned to the bucket by other processes. The semaphore class provides several built-in methods for working with semaphores: new(), get(), put() and try_get().

A mailbox is another built-in class that allows messages to be exchanged between processes. A message can be added to the mailbox at anytime by one process, and retrieved anytime later by another process. If there is no message in the mailbox when a process tries to retrieve one, the process can either suspend execution and wait for a message, or continue and check again at a later time.

Mailboxes behave like FIFOs (First-In, First-Out). When the mailbox is created, it can be defined to have a bounded (limited) size, or an unbounded size. If a process tries to place a message into a bounded mailbox that is full, it will be suspended until there is enough room. The mailbox class also provides several built-in methods: new(), put(), tryput(), get(), peek(), try_get() and try_peek().

The Verilog "event" type is a momentary flag that has no logic value and no duration. The event type can be triggered, and other processes can be watching for the trigger. If a process is not watching when the event is triggered, the event will not be detected. SystemVerilog enhances the event data type by allowing events to have persistence throughout the current simulation time step. This allows the event to be checked after it is triggered.

Constrained random values. The Verilog standard includes a very basic random number function, called "$random." This function, however, gives very little control over the random sequence and no control over the range of the random numbers. SystemVerilog adds two random number classes, "rand" and "randc," using SystemVerilog's object class system. These classes provide methods to set seed values and to specify various constraints on the random values that are generated.

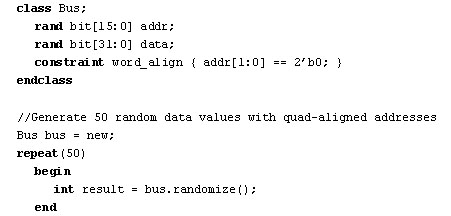

The following example creates a user-defined class called "Bus" that can generate a random address and data value, with limits on the value sizes. A constraint on the address ensures that the lower two bits of random address value will always be zero. The class is then used to generate 50 random address/data value pairs, using the randomize() method, which is part of the rand class.

Using the rand and randc classes and methods, much more elaborate random number generation is possible than what is shown in the preceding simple example.

Testbench program block. In Verilog the testbench for a design must be modeled using Verilog hardware modeling constructs. Since these constructs were primarily intended for model hardware behavior at various levels of abstraction, they have no special semantics to indicate how test values should be applied to the hardware. SystemVerilog adds a special type of code block, declared between the keywords "program" and "endprogram." The program block has special semantics and syntax restrictions to meet the needs of modeling a testbench. A program block:

Next

|

|

Quick

Links...  Search...  Veritools.com

LOGIN...

Click Here for

fast access to whitepapers and datasheets and to receive electronic Veritools' news, services and upcoming events.

New

Downloads...

|

Home

Home