|

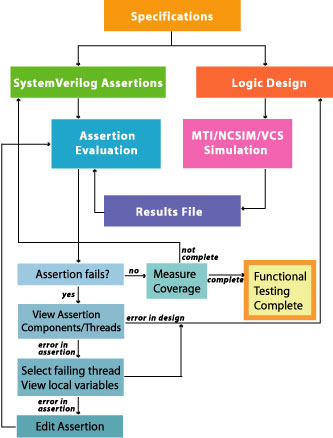

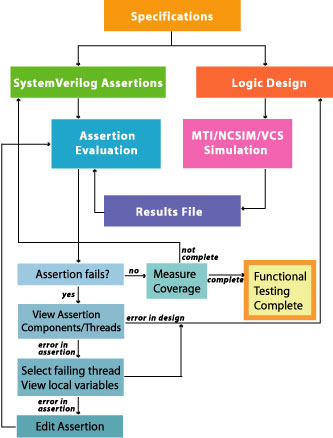

Functional Verification Coverage is now provided by VeritoolsVerify, with the addition of an extensive set of assertion evaluation analysis tools. Included are: Analysis of hold and fail conditions, display of assertions in the waveform window with the signals that caused the hold condition, and features that allow the user to do a "what if" analysis of the assertions that fail so that users can determine quickly why the assertion failed.

Why assertions are the future:

- In today's ASIC design environment, the percentage of successful ASIC tape outs has been in a significant decline over the past several years, in part due to the fact that ASIC designs have been getting progressively more complex. In an attempt to increase the success rate of new ASIC designs, many companies have been building in PSL and SystemVerilog assertions to their designs in order to do a more thorough job of verification. Today's designs can easily have over 20,000 lines of assertion code in the larger ASIC designs. It is expected that the next generation of designs will have over 100,000 lines of assertion code. Design managers and design engineers find that it is generally getting harder to manage such large amounts of assertion code and to see what the exact assertion coverage really is. With increasing numbers of lines of assertion code, it is difficult to even verify that the assertions are actually testing exactly what the design engineers had intended these assertions to test.

“Veritools integrates assertion support into VeritoolsDesigner in two ways: 1) analysis of simulation results from simulators that can support assertions as part of their input language, and 2) analysis directly from any waveform file generated from Verilog/VHDL or SystemVerilog by using a new tool that has been added to the VeritoolsDesigner, the Veritools' Assertion Analyzer.”

|

Home

Home Products

Products